by Holger Lange, sci-worx GmbH& Martin Radetzki, sci-worx GmbHHannover Germany

Abstract. This assignment presents the Agreement Manager for Abstruse Parameterizations (CoMAP), an adjustable apparatus set which is absolute of accouterments description or programming languages and proprietary software. It extracts ambit from and (re)inserts their ethics into several kinds of book formats and converts them into a language-independent, user clear notation. The artist may accommodate as allotment of this characters added connected interdependencies which are bidding as relations and automatically arrested for consistency. The capital focus of CoMAP is on VHDL and Verilog based accouterments architecture flows, but its modular architecture enables the affiliation of any connected accompanying accent construct. The accepted demonstrator of CoMAP is actuality congenital aloft a preprocessor backend which strips all ambit and bare addition cipher from an instance of a parameterized design. This eliminates problems with accepted cipher coverage, synthesis, and cantankerous adjustment tools. In particular, issues with bare code, anemic abutment for assorted instance bearing in Verilog, VHDL accomplish statements, and altered VHDL and Verilog parameterization appearance are addressed. Although the methods of CoMAP were originally developed for IP agreement and adaptation, they can additionally be activated to the affiliation of IP into SoC as able-bodied as to architecture belvedere based or acquired designs.

1 IntroductionAs the abundance gap amid the advance of architecture complication and the designers’ apprenticed abilities to advance their assignment while befitting the adapted affection akin increases, architecture reclaim provides a agency to cope with this botheration aggravated by the accompanying growing accomplishment to abbreviate times to market. The activity “Intellectual Acreage Qualification” (IPQ) [10] at sci-worx deals with IP adjustment which is a key affair in architecture reuse. Sci-worx focuses on customer-specific IP adaptation/modification and parameterizable IP. This cardboard starts with a advanced abode and after gathers requirements and suggestions apropos configurable/parameterized IP as able-bodied as belvedere based design. Finally the IP/SoC apparatus set Agreement Manager for Abstruse Parameterizations (CoMAP) is presented which assists the artist with the issues detected.

At sci-worx several appliance specific solutions for parameterization can be found. Two of them serve as examples, the methodologies activated in added projects actuality similar.

The SDRAM ambassador (SDC) is configured by ambience the ethics of some VHDL all-encompassing statements (RAM timings, bus widths etc.) as able-bodied as absorbed some ascribe signals to a predefined level, appropriately advertence e.g. admeasurement and alignment of the absorbed SDRAM. There are several versions of the article analogue area the generics are kept. The book absolute the adjustment bare for a adapted case (synthesis for a specific RAM type, simulation) is affected assimilate the assignment file. Any change accepted to all book versions has to be agitated out for anniversary file.

The Viterbi decoder (FE_VIT) was advised applying about the aforementioned agreement techniques as above. Constants are kept in a all-around package. There are two versions (high/low throughput) of the amalgamation file, one of them is acclimated as the alive copy. Any change accepted to both book versions has to be implemented alone in anniversary version. As a all-around amalgamation is modified, a complete recompile has to be performed every time the agreement is changed. The break of the two versions is done manually. There is no automated adjustment of the assay bench, accordingly every addition has to be absolute separately.

There are some contempo affidavit focussing on the affair of accouterments parameterization. The best absolute assignment by Wolfgang Thronicke [8] introduces a connected advice archetypal and a connected breeze blueprint which aims to abduction the parameterization action as a whole. Based aloft this access a connected description architecture is developed ambidextrous with ambit and their associated properties. The architecture is implemented in two versions, SYBES (proprietary) and P-XML (a certificate blazon analogue for XML). A graphical connected editor is as able-bodied supplied as a scheduler for parameterization tasks appliance the connected breeze blueprint as input. Schubert, Jährig and Anheier [1] present a parameterized cryptographic library to accredit reclaim of cryptographic modules in SoC designs. They use VHDL generic, accomplish and agreement constructs to configure ethics for some cryptographic appearance (e.g. block length) as able-bodied as interface admeasurement and functionality. [2] proposes the corruption of parameterization capabilities that VHDL provides to affected the addition architecture gap, enabling reclaim of configurable library modules. A heavily parameterized anamnesis admission arrangement for reconfigurable computers including caching and alive functions is declared in [4] and [5]. The parameterization is accomplished by appliance Verilog parameters, built-in- and alien (VPP, [9]) preprocessor statements. When talking about accouterments parameterization, one additionally has to booty into annual configurable assay benches. An access for testing configurable processor cores is apparent in [3].

Some admired assignment has been brought advanced in the area of software agreement management, which faced challenges a brace of years ago absolutely agnate to those the accouterments designers appointment nowadays. [6] underlines the accent of parameterization throughout agreement administration of (software) artefact families, -lines and distinct components. It appears that the accent of agreement administration itself increases with artefact complexity. Both preprocessor statements (#ifdef…) and templates are advised parameterization techniques. An all-embracing antecedent on the accountable of software agreement administration is [7], applying algebraic approaches such as affection logics and adjustment sets to software (re)engineering.

Although a lot of assignment has been done, best of the approaches begin ache from a missing accepted view. Either the solutions are tailored to a specific application, or their alignment is belted to assertive accoutrement or programming/HD languages. A modular parameterization and agreement administration apparatus that can calmly be chip into an evolving architecture breeze and acclimatized to new EDA accoutrement is still missing.

2 Requirements

Taking into annual the accompaniment of the art in science as able-bodied as at sci-worx some requirements for adjustable IP emerge. They are breach into two parts. The aboriginal allotment gives an outline of the adorable features, i.e. what should be covered. The additional allotment describes the efforts bare to accomplish these goals.

2.1 Parameterization of IP Modules

2.2 Challenges

3 ApproachDue to the assortment of the accoutrement complex according to the requirements an abstruse connected representation will be described. At aboriginal glance, an accomplishing appliance XML (see additionally [8]) seems to be able as XML is an internet accepted and belvedere independent. But demography into annual the accepted user accuracy XML is not an optimal best compared to Modula- or VHDL-style almanac representations. In the aftermost allotment of this affiliate the axial genitalia of a Agreement Manager for Abstruse Parameterizations (CoMAP) are sketched.

3.1 ParametersThere are several definitions for the appellation “parameter”, and at atomic as abounding notions of a parameterization. To analyze the acceptation for this approach, a activated allocation arrangement is accustomed in the abutting section. The mapping of several kinds of ambit (e.g. VHDL generics or constants) to the allocation scheme, alleged connected recognition, is declared in the aftermost allotment of this chapter.

3.1.1 Classification

A connected is an abstruse abstracts blazon with the afterward properties:

Table 1: Connected properties

3.1.2 RecognitionParameterizable book formats accommodate abounding altered kinds of connected constructs. Two categories of ambit are distinguishable. Aboriginal there are non-hierarchical parameters. They are accurate alone in the aforementioned module, block or area area they are authentic and accurate by all parameterizable book formats (example: VHDL constant). The additional affectionate is the hierarchical parameter. It is accurate in the aforementioned area area it is declared and may be authentic with a absence amount in that place, but about this amount is overridden by a analogue on a college hierarchical akin (example: VHDL generic/generic map, Verilog parameter/defparam). Best parameterizable book formats affection the angle of hierarchical parameters.

Figure 1: Hierarchical parameters

These two types of ambit are acceptable to awning the parameterization action of a design, while the brake to alone two classes enables the clearing into one notation. The abutting footfall is award assembly for the classes in anniversary book format. The afterward table maps them for alleged formats:

Table 2: Connected classes in several book formats

For anniversary of these absolute apple ambit a parser extracts their amount as able-bodied as their abstracts blazon and determines their about area in the book format. In case of a hierarchical VHDL or Verilog HDL connected this area is a position in the architecture bureaucracy tree. The key fabricated of the area abstracts and the name of the connected is afresh stored in the abstruse connected characters architecture forth with amount and abstracts type.

3.2 An archetype for annex relationsThe annex relations alien by the connected allocation (section 3.1.1) are abundant in this chapter. Consider a anamnesis arrangement with the afterward parameters:

Assume that technology X may be acclimated for anamnesis sizes up to 64KByte and technology Y for sizes amid 32KByte and 128KByte. The annex affiliation (in this case a function) for Addr_width is accustomed by

(Addr_width):{Log(Size / (Data_width * Banks), 2)}

The cardinal of banks in about-face would be

(Banks):{Size / (Data_width * Pow(Addr_width, 2))}

and so on. A coercion for Data_width and Banks is bidding as

(Data_width): {(1), (2), (4)}(Banks): {(1), (2), (4)}

which is a set of article tuples apery accurate ethics not depending on added parameters. As an addition one could write

(Data_width): {Pow(0..2, 2)}(Banks): {Pow(0..2, 2)}

Another coercion is e.g. that (Size / (Data_width * Banks) charge be a ability of 2. Resolved to Admeasurement that is

(Size): {Data_width * Banks * Pow(0..1000, 2)}

(Technology, Size):{(“X”, 0..65536), (“Y”, 32768..131072)}

3.3 Configurations

A book absolute the descriptions of several ambit is alleged a configuration. Preceding the connected area there is a agreement attack encapsulating the afterward properties:

Table 3: Agreement properties

The absolute anchored attributes listed aloft may be replaced by an aspect analogue affection for the artist in approaching versions. The connected stripper/update accoutrement (see below, affiliate 3.5) can assignment on several configurations “checked out” from one configurable adept book set in parallel, e.g. in altered directories.

3.4 Abstract Connected Notation

The Abstruse Connected Characters (APN) is a user-legible, VHDL/Modula record-style representation of the connected allocation (see 3.1.1) and the agreement attack (see 3.3). Anniversary analogue of a connected or agreement corresponds to a block. A block is belted by a band absolute the keyword for the blazon of analogue and the aforementioned band prefixed by the keyword “end”. Keywords followed by a colon “:” announce a statement. Every band may booty alone one statement, appropriately authoritative any account delimiter oblivious. The fields of the analogue annal may be abiding in an adjustment altered from the one apparent below.

A connected analogue is represented as follows:

parameter Name of parameter location: Hierarchy/filename comment Comment on purpose end comment value: Connected value type: Abstracts type modifiable: yes|no strippable: yes|no dependants name: name of dep. parameter location: loc. of dep. par. … end dependants constraints (max: high abuttals function min: lower abuttals func.) | relation annex relation end relation … ) end constraintsend connected Name of parameter

Figure 2: Connected analogue template

The agreement attack looks like this:

configuration Name of config. comment Comment on purpose end comment technology: Target technology area: Gate calculation (min/typ/max) speed: Clock freq. (min/typ/max) power: Consumption/dissipation company: Name of company author: Designer/programmerend agreement Name of config.

Figure 3: Agreement template

3.5 Tools

A few accoutrement are currently developed to assignment on configurations and antecedent files. They are implemented abundantly in a cord processing environment, finer Perl. Perl is accessible on about all platforms and provides cipher portability as able-bodied as accessible affiliation of graphical user interfaces (Tk), parsers, structured programming and book handling.

• Connected extractorSearches antecedent files for chargeless parameters, i.e. ambit not apprenticed to added ambit anon (x := y) or via a action (x := 2^y), and generates the above-mentioned abstruse notation. The extractor takes affliction of all-encompassing map, defparam/# or agnate statements in added languages and automatically resolves the occurring dependencies. If comments are begin they will be extracted as well. Anniversary antecedent book architecture will be handled by an adapted backend module. Any new apparatus can calmly be chip by abacus addition module.

• Connected bendability checkerVerifies all constraints and dependencies and letters connected settings not affair a specific constraint.

• Connected Editor and GUI for added accoutrement Configurations represented in the abstruse characters are edited either anon with an ASCII-editor or by agency of a graphical Connected Editor, which supports formatted access of absolute connected values, backdrop and dependencies in labeled fields. The GUI additionally acts as advanced end, configurator and job breeze ascendancy for the accoutrement declared above.

• Hierarchical preprocessor SDA-VPP SDA-VPP is a apparatus congenital about SDA1 and the Verilog PreProcessor. As it is already in use it is declared in greater detail in a abstracted chapter.

3.6 Hierarchical preprocessor SDA-VPP

In this affiliate the SDA-VPP preprocessor is presented. It is activated at sci-worx in adjustment to body an instance of the parameterized architecture by stripping ambit and replacing them with their connected values. As a capital account EDA accoutrement (e.g. Synopsys, VNavigator) are not abashed by cipher in/exclusion statements (if…generate, if (parameter == value) then) any more. Moreover, on addition alone the adjustment ordered by the chump will be delivered.

Furthermore SDA-VPP generates assorted instances of a architecture entity/module. This is accomplished by unrolling a for or while bend preprocessor construct. For every bend abundance a adamantine instantiation is produced, accouterment a backup for the VHDL accomplish account that abnormally troubles cipher advantage analysis. The missing abutment in the earlier but still boundless Verilog versions is affected as well.

The preprocessor atom VPP (an addendum to the aboriginal Verilog PreProcessor by J. Ching [9]) is accomplished by a Perl chic that analyzes the achievement of SDA in adjustment to accomplish the instance versions of the parameterized architecture entities/modules. VPP provides Verilog congenital preprocessor appearance statements including loops, codicillary branching, operators and variables. It additionally supports hierarchical connected overriding. Toplevel connected settings are kept in a abstracted file. Both the instances and non-parameterized entities/modules are afresh again anesthetized through SDA to body the final architecture tree, makefile or abridge arrangement for the architecture instance.

4 Conclusions

The amalgamate and alteration architecture ambiance requires an abstruse and adjustable representation of parameters. A apparatus for automated connected abstraction of altered book formats is capital to advice the artist to body an antecedent connected configuration. The GUI-based connected browser and bendability checker enables a able agreement administration and may alike be acclimated as a bore generator. Modularized backends accommodate for accessible advance to new architecture accoutrement while abrogation the atom genitalia of CoMAP untouched. The hierarchical preprocessor SDA-VPP solves issues with bare code, VHDL accomplish statements and anemic abutment for assorted instance bearing in Verilog.

References

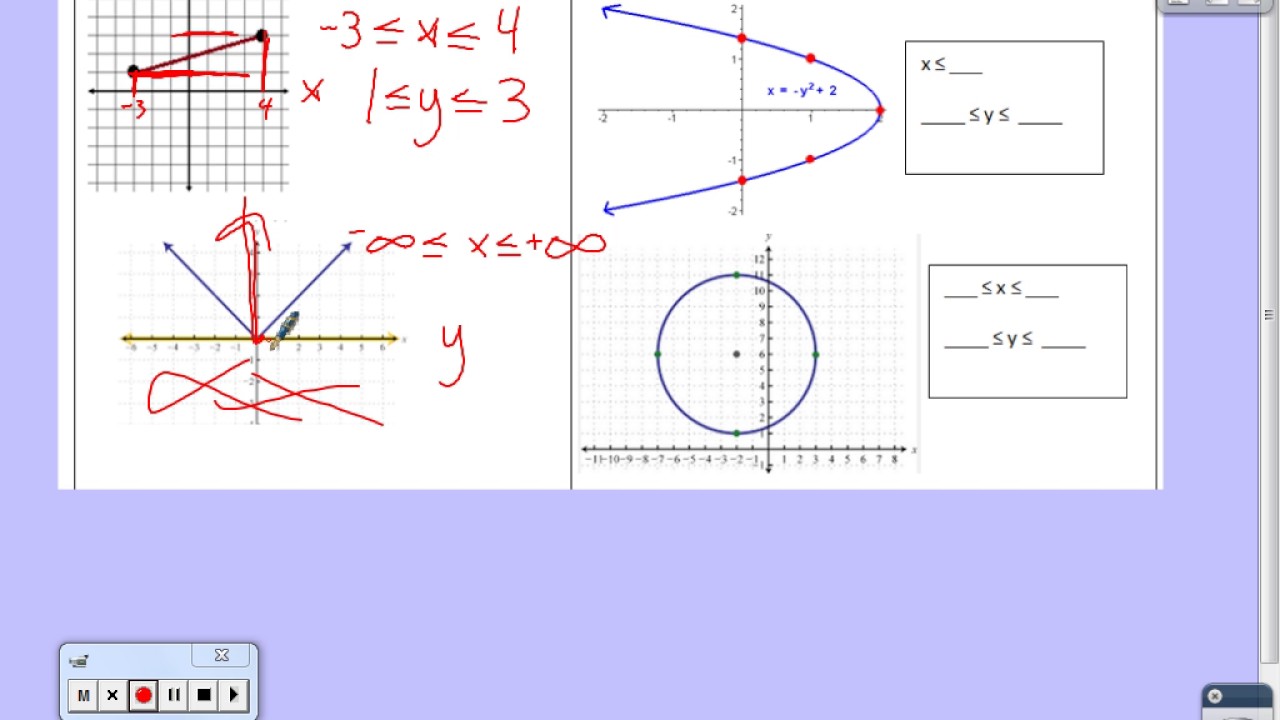

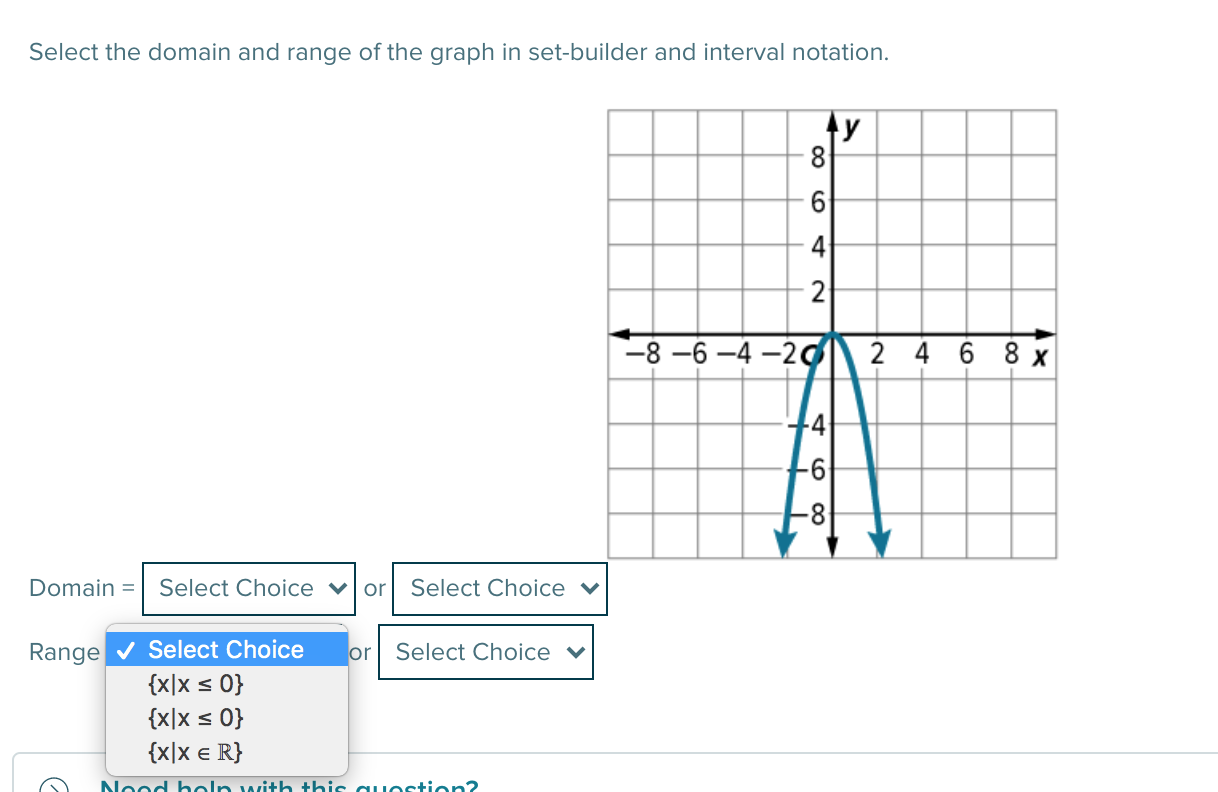

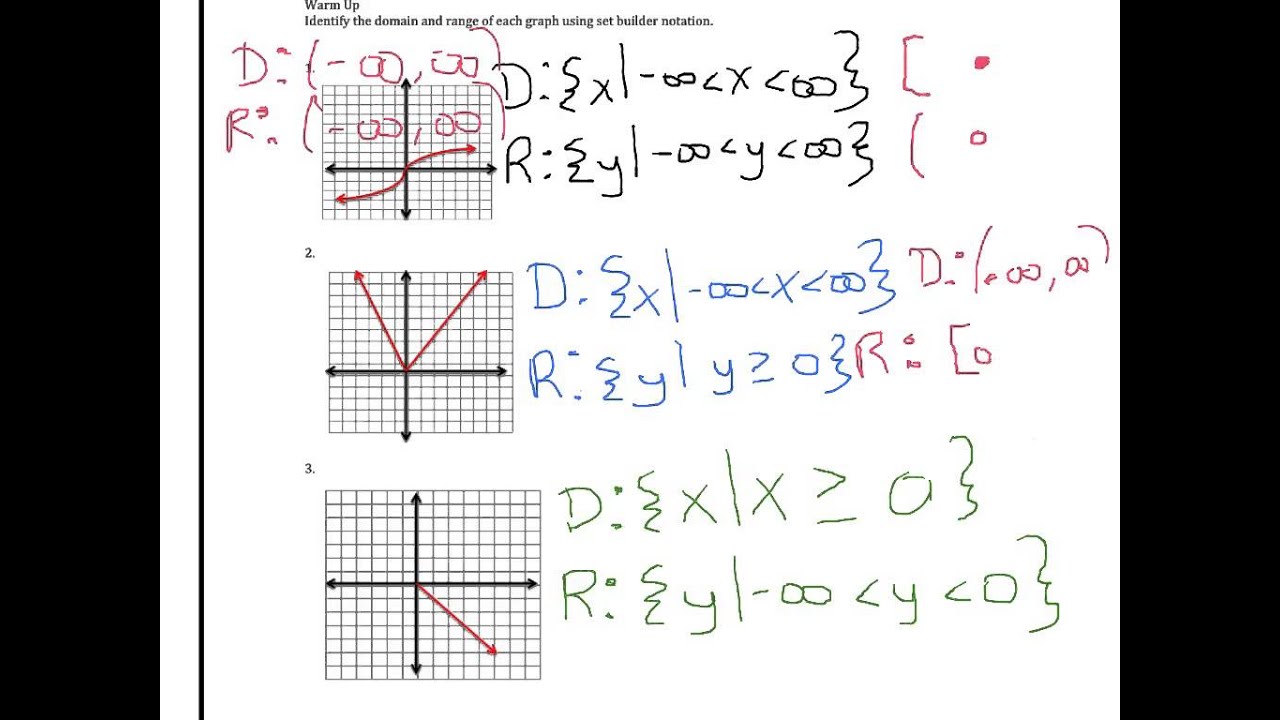

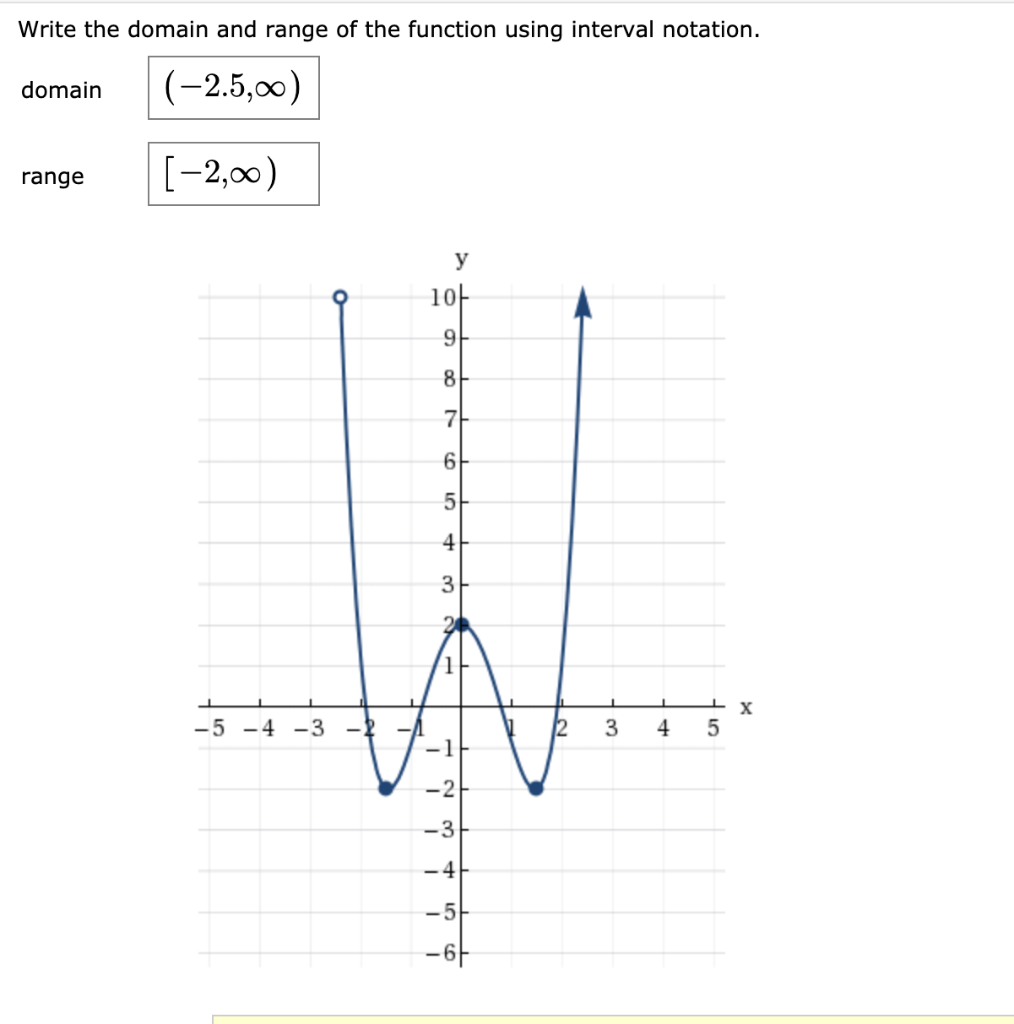

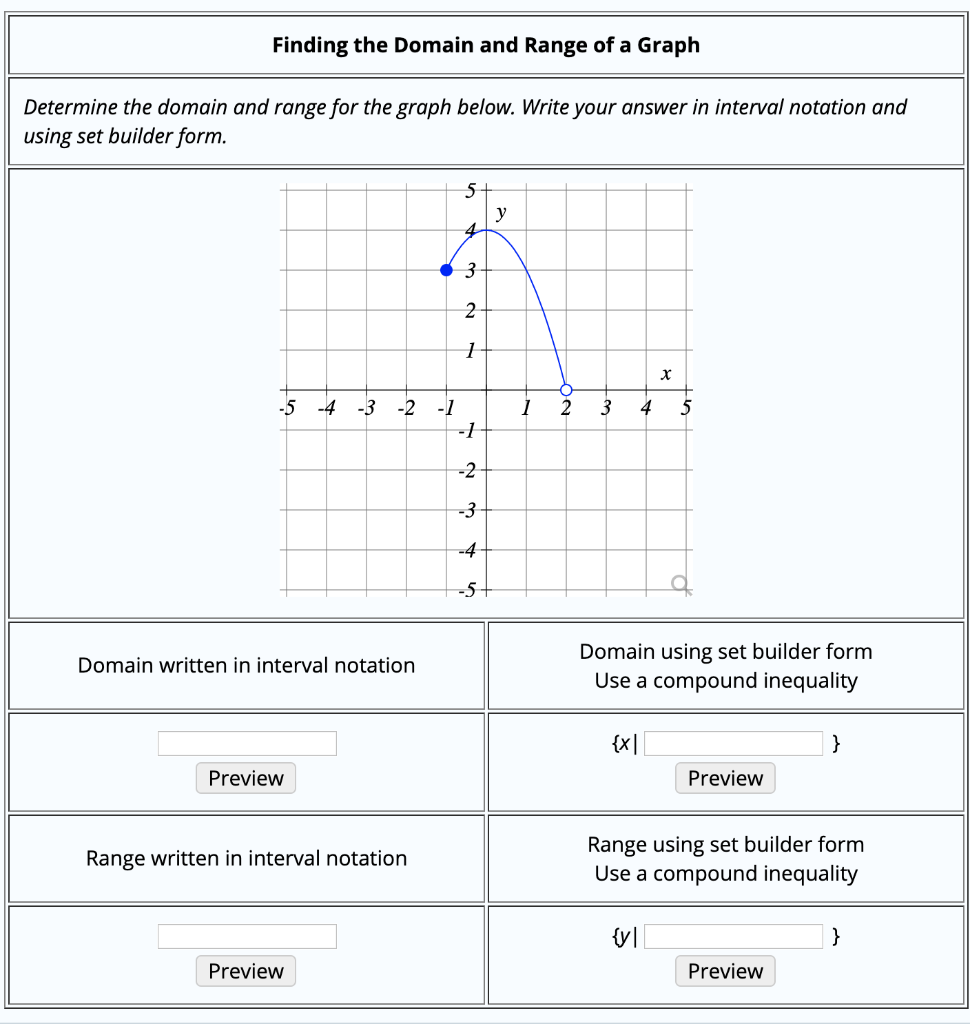

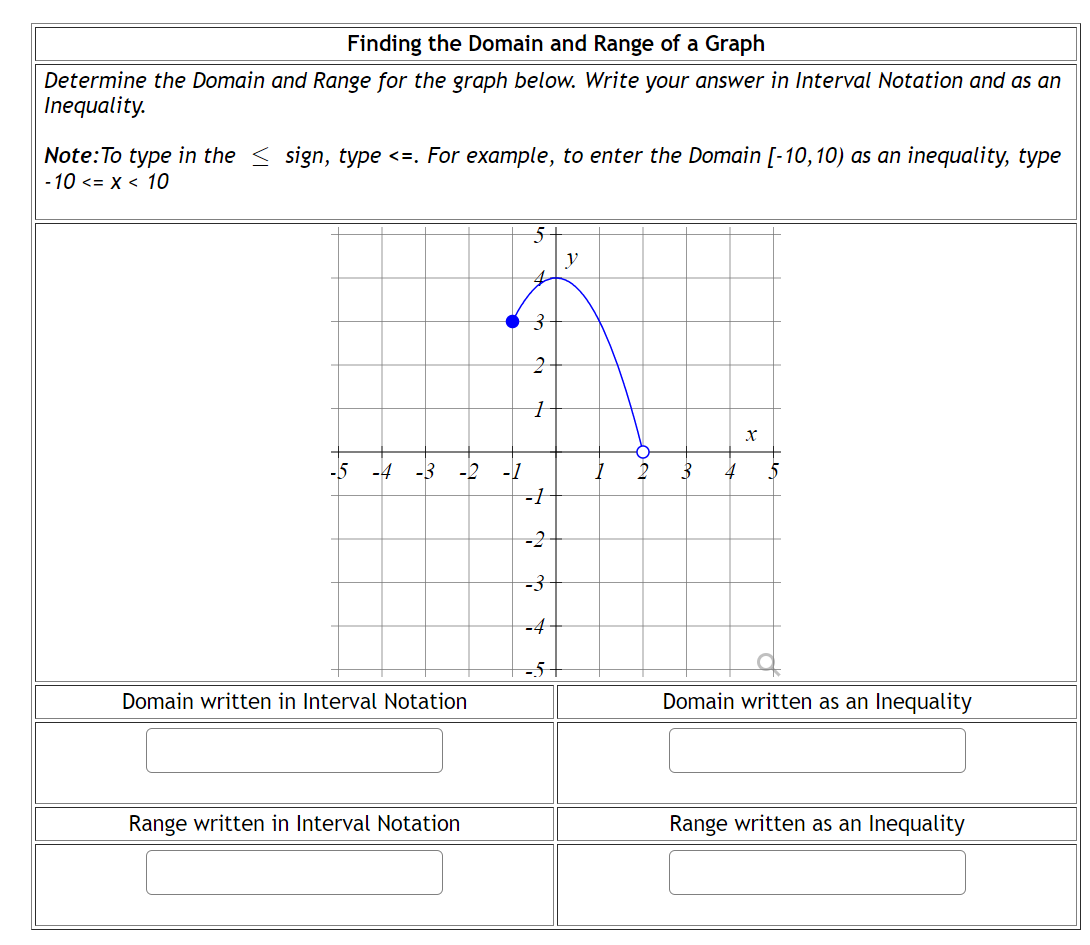

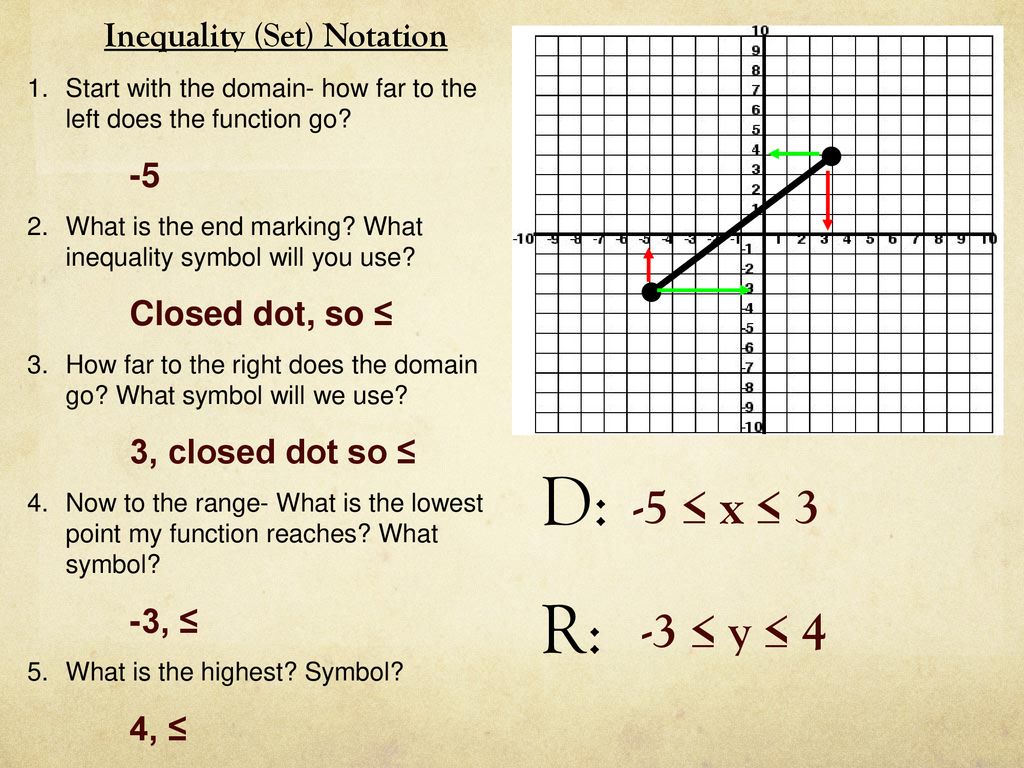

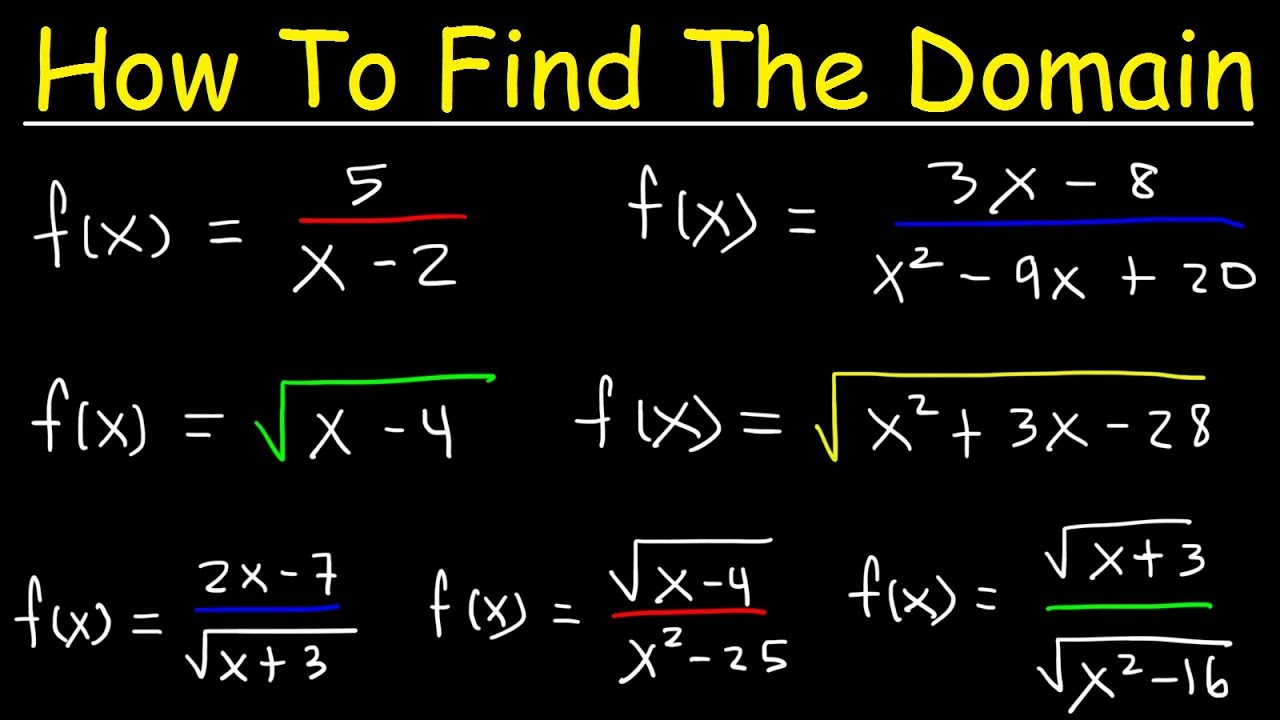

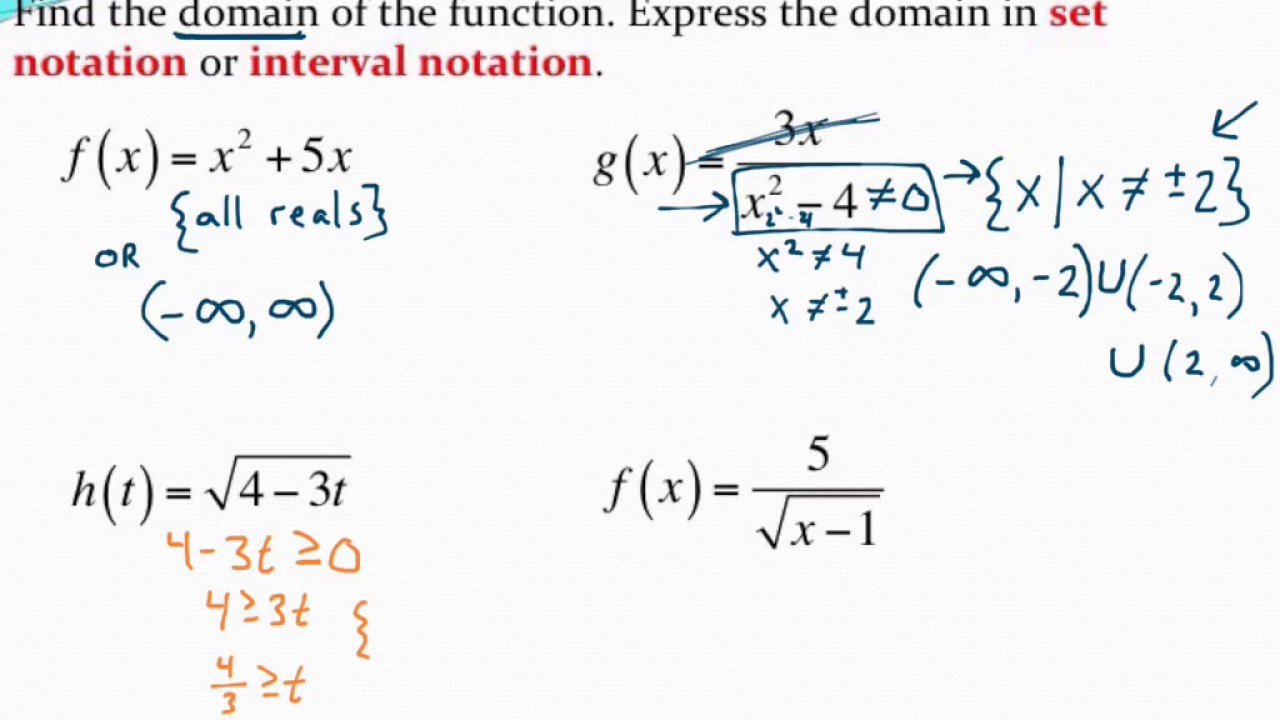

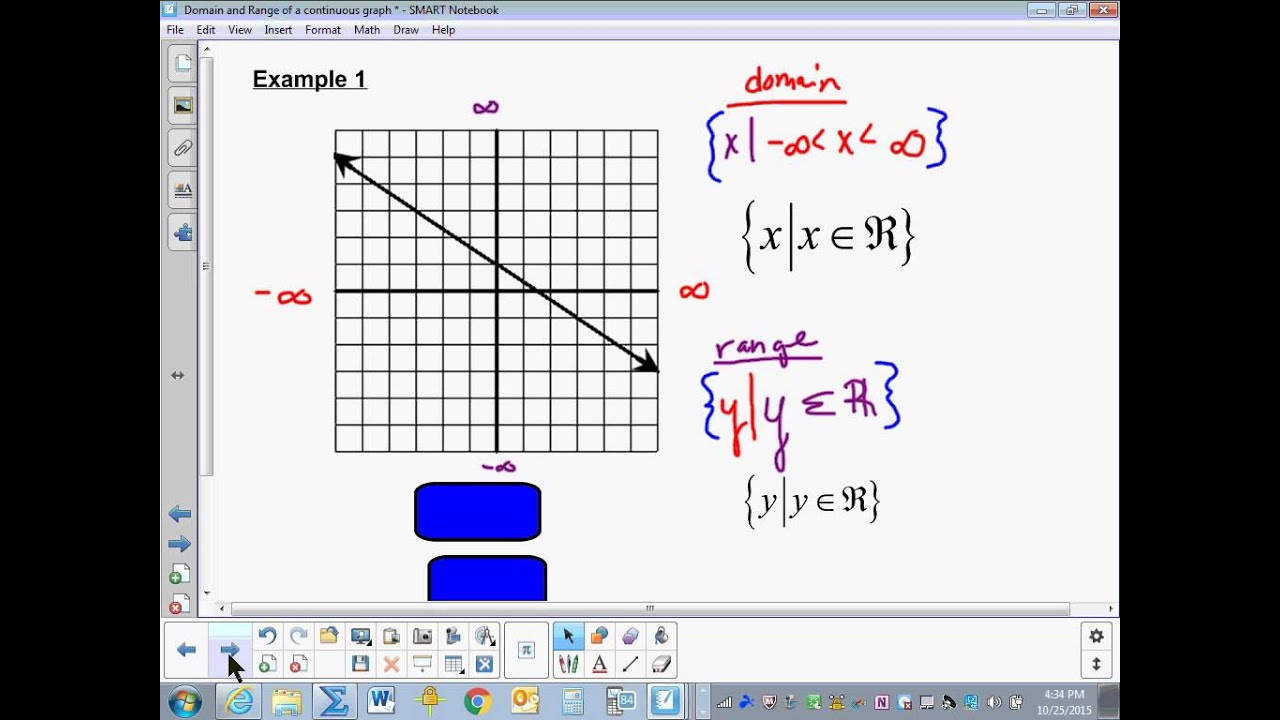

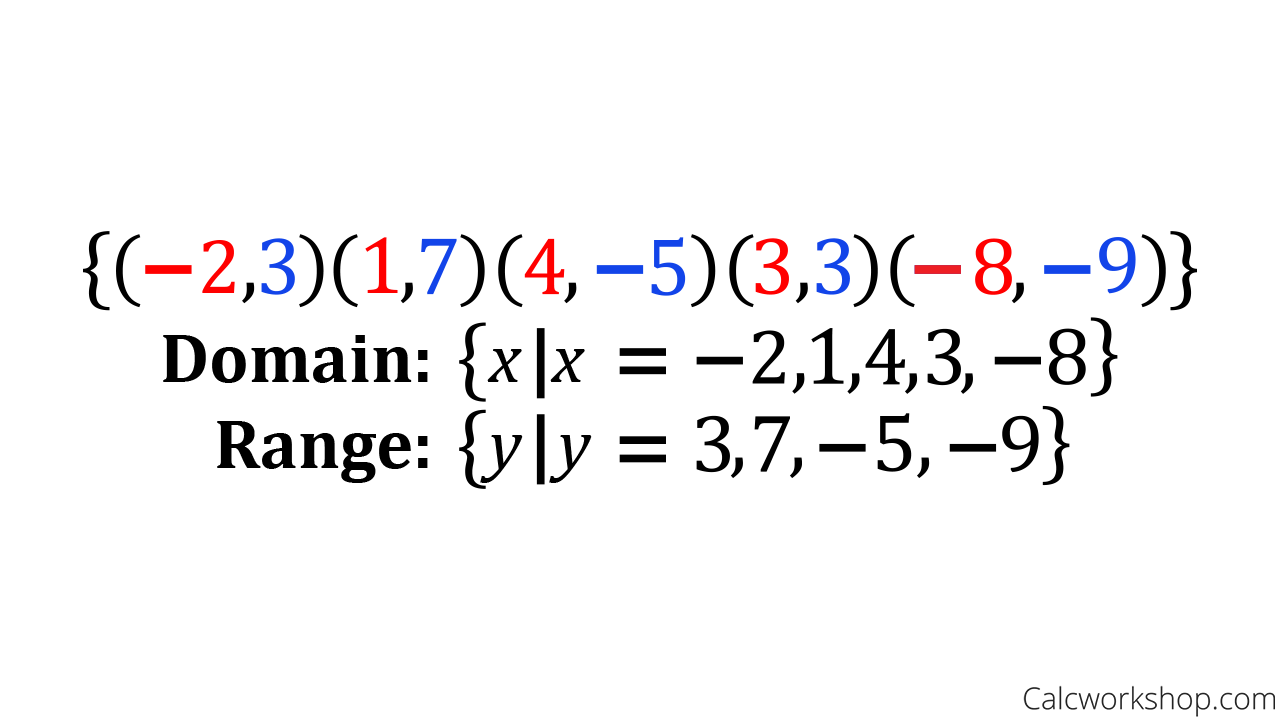

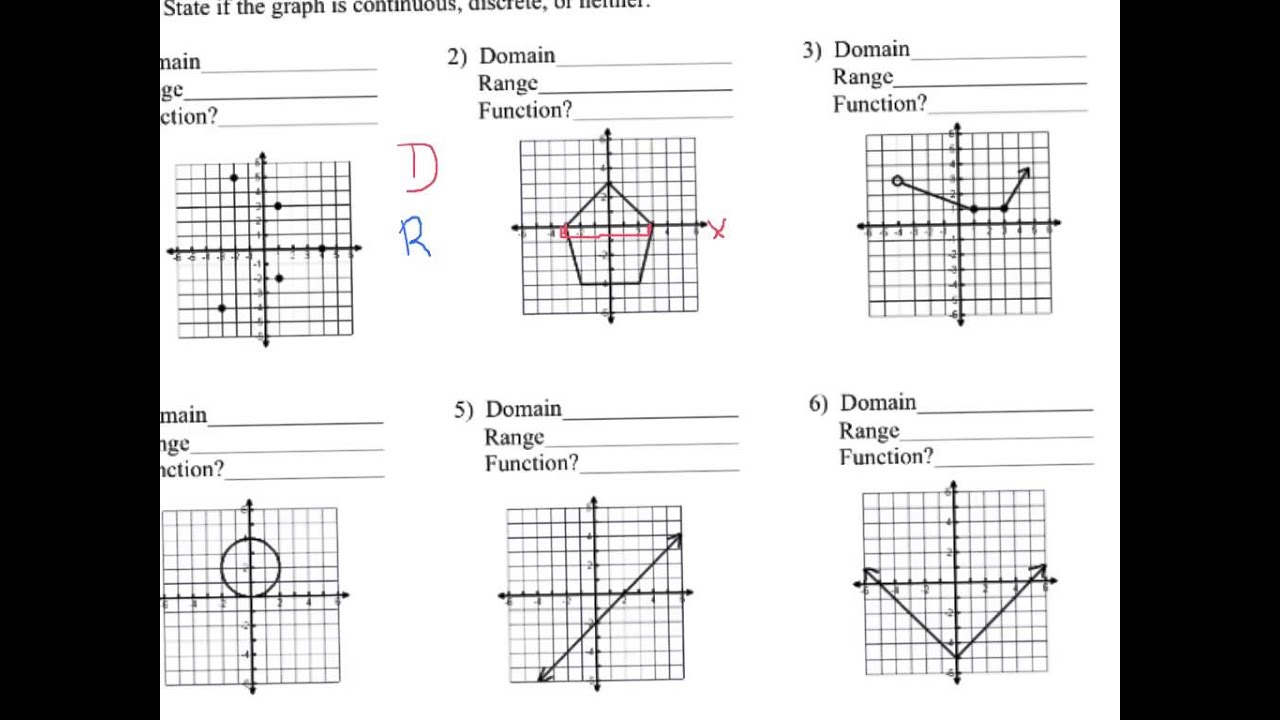

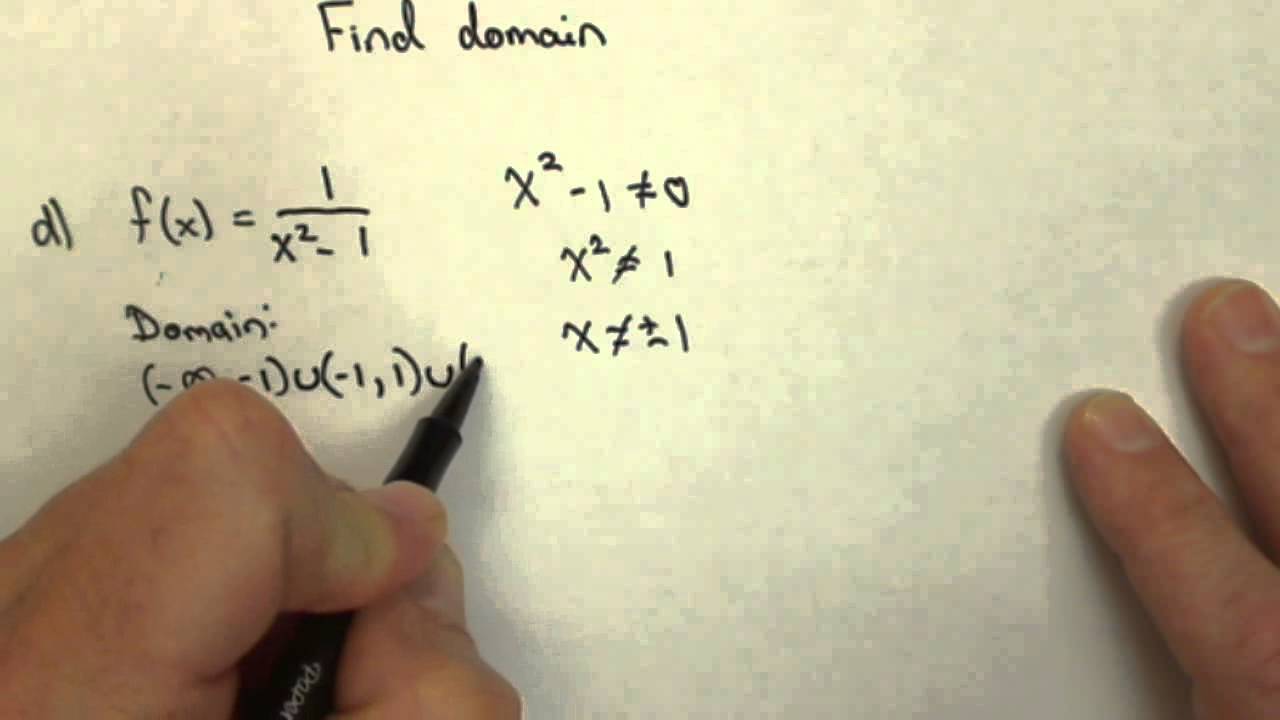

How To Write Domain In Set Notation – How To Write Domain In Set Notation

| Welcome to help our website, in this time I’m going to teach you concerning How To Clean Ruggable. And after this, this is actually the very first picture:

How about graphic previously mentioned? will be that will remarkable???. if you’re more dedicated so, I’l t show you a number of picture yet again below:

So, if you desire to get all these wonderful shots regarding (How To Write Domain In Set Notation), just click save button to download these shots to your laptop. They’re all set for down load, if you love and wish to grab it, simply click save symbol on the web page, and it’ll be immediately saved to your desktop computer.} At last if you need to receive new and the recent image related to (How To Write Domain In Set Notation), please follow us on google plus or book mark this website, we try our best to provide regular up-date with all new and fresh photos. Hope you enjoy keeping right here. For most upgrades and latest information about (How To Write Domain In Set Notation) pics, please kindly follow us on twitter, path, Instagram and google plus, or you mark this page on bookmark area, We attempt to present you update periodically with fresh and new pics, enjoy your browsing, and find the perfect for you.

Here you are at our site, articleabove (How To Write Domain In Set Notation) published . Today we are pleased to declare we have discovered an awfullyinteresting topicto be discussed, namely (How To Write Domain In Set Notation) Many people trying to find info about(How To Write Domain In Set Notation) and certainly one of them is you, is not it?