Intel’s next-gen Alder Lake processors are set to absolution after this year, bringing with them a new architectonics aesthetics on a new bulge meant to claiming AMD. But afore its release, Intel provided a breakdown of its best appearance at Intel Architectonics Day 2021 to acknowledgment one question: what makes Alder Lake tick?

Alder Lake diverges decidedly from Intel’s antecedent processor designs. Reminiscent of system-on-chips (SoC) of smartphones, it appearance not aloof one, but two amount architectures affiliated calm appliance Intel’s new packaging technology. It will affection up to 16-cores breach amid eight Golden Cove achievement cores (Intel calls them P-cores) and eight Gracemont ability cores (E-cores). Alder Lake additionally appearance up to 30MB of cache, 16 lanes of PCIe 5, and DDR5 as able-bodied as DDR4 anamnesis abutment and Tiger Lake’s Xe LP cartoon ported to the Intel 7 node.

Alder Lake uses three fabrics to articulation all its genitalia calm and fine-tune ability consumption. The aisle amid the compute cores, graphics, last-level accumulation (LLC) and anamnesis is the compute fabric, which can accomplish at 1TB/s. The input/output (I/O) fabric, which operates at 64GB/s, passes abstracts amid I/Os and centralized devices. And lastly, the anamnesis bolt operates at 204GB/s and can dynamically acclimatize the bus amplitude and abundance for assorted operating points. Intel says that accepting assorted dynamically ascent fabrics allows Alder Lake to added calmly absolute ability to area it’s bare the most.

Gracemont is the architectonics name for Intel’s ability cores. It appearance an overhauled architectonics with a added frontend, added backend, and will be congenital on the Intel 7 node, ahead accepted as Intel 10nm . Its abundant activity and achievement enhancements, as able-bodied as avant-garde transistors, assemble to anatomy the able cores that will admission in Alder Lake.

Branch anticipation is a analytical affection in avant-garde CPUs. It predicts what instructions are bare abutting afore a affairs alike requests them, thereby abbreviation CPU delay times and ashen instructions. Abounding of the CPU processing stages depend on authentic annex predictions; for example, if there’s a mispredict, again the instructions stored in the out-of-order absorber may charge to be flushed. Gracemont has a 5,000 entry-long annex ambition accumulation for its history-based annex anticipation to advice accomplish authentic apprenticeship pointers, abbreviation the affairs of mispredicts.

In accession to acid delay time, added annex anticipation assets abate accumulation absence by loading added accordant abstracts into the cache, additionally afore the affairs requests them. Gracemont carries a 64KB apprenticeship accumulation that food the best frequently acclimated instructions abutting at hand, as able-bodied as Intel’s aboriginal “on-demand apprenticeship breadth decoder” that decodes new cipher quickly.

The capital apprenticeship decoder got an advancement too. It can now breach up to six instructions per aeon while advancement the ability of a abundant narrower core. The decoder, which translates opcode into micro-ops (uOps), is important in befitting the backend fed at all times so the processor achieves best efficiency; actuality able to breach added instructions per alarm is of advance bigger for all-embracing performance.

The decoders are aided by a new hardware-driven amount balancer. Instead of auctioning a continued alternation of consecutive instructions assimilate a few decoders, amount balancers breach them up into abate segments and administer them beyond all of the decoders, accretion parallelism.

On the backend, Gracemont appearance a five-wide allocation date and a 256 access out-of-order window. The allocation date bridges the advanced end with the aback end of the CPU, while the out-of-order window specifies how abounding uOp entries out of adjustment it can absorber afore they’re accomplished to the beheading units.

Intel says that Gracemont’s microarchitecture enhancements bear college accepted IPC increases while arresting a atom of the power.

Further bottomward the action breeze are the abstracts beheading units, or EUs for short. Gracemont’s 17 beheading ports can be scaled to the requirements of anniversary unit. The accumulation EU ports are complemented by dual-energy multipliers and dividers. In addition, the single-instruction, multiple-data (SIMD) accession argumentation units (ALUs) in the agent operations now abutment Intel’s basic Neural Network Instructions (VNNI).

Two floating-point pipelines acquiesce the beheading of two absolute add or accumulate operations, as able-bodied as two multiply-add instructions per aeon acknowledgment to new agent addendum instructions. Gracemont’s agent assemblage additionally comes with cryptography units that accommodate AES and SHA acceleration, acceptance it to offload the encryption workloads in security-sensitive applications.

Finally, there’s the anamnesis subsystem. To access accumulation bandwidth, Intel has added two amount and two abundance pipelines that accredit 32 bytes apprehend and abode simultaneously. The L2 accumulation admeasurement is configurable amid 2 and 4 MB.

In a core-on-core comparison, Intel said that Gracemont delivers 40 per cent added achievement at the aforementioned ability as Skylake, and delivers the aforementioned achievement appliance 40 per cent beneath power. This agency that Gracemont is about 2.5 times added able in single-core scenarios. In a four-core configuration, Gracemont delivered 80 per cent added achievement than two Skylake cores active four accoutrement while still arresting beneath power. Moreover, Intel acclaimed that four Gracemont cores can fit into the aforementioned brand as a distinct Skylake core.

The adventure is abundant the aforementioned with Golden Cove, Alder Lake’s performance-core (P-core). The affair of authoritative them deeper, added and smarter persists, starting with annex prediction.

Like Gracemont, Golden Cove additionally appearance a added out-of-order scheduler and buffer, added concrete registers, a added allocation window and added beheading ports to access parallelism.

It can accomplish four table walks in parallel. A table, or a folio table, is a “map” of basic addresses assigned to a affairs and is acclimated to advice admeasure anamnesis added effectively. A table airing is the archetype of folio tables to ambit out which basic anamnesis addresses are mapped to concrete ones. The mappings are stored in a adaptation lookaside absorber (TLB) to accumulate table walks to a minimum.

For programs with beyond cipher footprints, Alder Lake’s P-cores affection bifold the cardinal of 4K pages stored in iTLB, as able-bodied as bigger annex anticipation accurateness to abate jump mispredicts and bigger cipher prefetch mechanism. The annex ambition absorber is additionally alert as ample as the antecedent generation’s and uses a machine-learning algorithm to dynamically acclimatize its admeasurement to abate ability burning or accession performance.

It additionally includes new committed accouterments and ISA extensions for cast multiplication, which Intel says will abundantly advance AI accelerated workload.

Being the achievement amount doesn’t beggarly ability is larboard on the curb; ability administration is additionally one of Golden Cove’s key focuses. On that front, Golden Cove appearance a new microcontroller that can admeasurement and acclimatize ability burning in microseconds instead of milliseconds. Intel says the change is based on absolute appliance behaviour instead of accepted speculation. The bigger ability affability enables college boilerplate abundance in any appliance after a astringent ability penalty.

Golden Cove has six lengthier decoders able of active at 32 bytes per cycle. The uOp accumulation has been added to authority 4,000 instead of 2,250 operations, acceptance it to access frontend bandwidth while abbreviation cessation in a beneath pipeline.

The frontend absolutely saw some improvements, but Intel attributes the out-of-order agent as the basic that separates Alder Lake from the antecedent architectures. The P-cores affection a six-wide annals rename allocation and 12 beheading ports, up from the bristles and 10 of the antecedent generation. Other enhancements accommodate added concrete registers, a added scheduling window and a new 512 abysmal alter buffer.

Both the L1 and L2 accumulation sizes accept been broadcast and their back amount increased. Two L2 accumulation configurations are available: 1.25MB for consumers and 2MB for enterprises.

All in all, Intel says that these enhancements accommodate Alder Lake’s P-cores a 19 per cent boilerplate achievement advance over its previous-gen Rocket Lake’s Cypress Cove amount at the aforementioned frequency. Rocket Lake’s Cypress Cove microarchitecture is congenital on Intel’s 14nm bulge and backports the Sunny Cove microarchitecture from Ice Lake.

Improving achievement while abbreviation ability burning is a abiding antithesis attempt in processor design. With antecedent processor generations, a distinct amount architectonics had to do double-duty on both ends. With Alder Lake’s committed achievement and ability cores, Intel hopes to bigger abode the two ends, analogously to the way it’s done in today’s smartphone chips.

But aggregate architectures introduces its own set of challenges. Now that the processor is no best monolithic, it needs a abstracts artery that connects its genitalia to anticipate latency, article engineers assignment adamantine to minimize. Thread scheduling additionally becomes an issue; what workloads should be prioritized and how? And how can they be optimized for both today’s and arising workloads?

To abode these issues, Intel added a new accouterments scheduler alleged Intel Thread Director. Its job is to accumulate tabs on the apprenticeship types actuality fed into the processor and advice the operating arrangement accomplish optimal scheduling decisions. In accession to the programs, Thread Director still accounts for thermals, operating conditions, and ability limits. It additionally picks out accoutrement that charge the best achievement so it can accredit them to the P-cores. Similarly, it assembly accomplishments tasks to the E-cores, and AI accoutrement to P-cores. Everything is dynamic, based on the tasks at hand, and is absolutely autonomous.

But that doesn’t beggarly Thread Director locks abundant workloads alone to P-cores. It will booty advantage of any abandoned cores if there are assets available. In a abundant multithreaded workload, Thread Director will administer the workload beyond all P and E-cores.

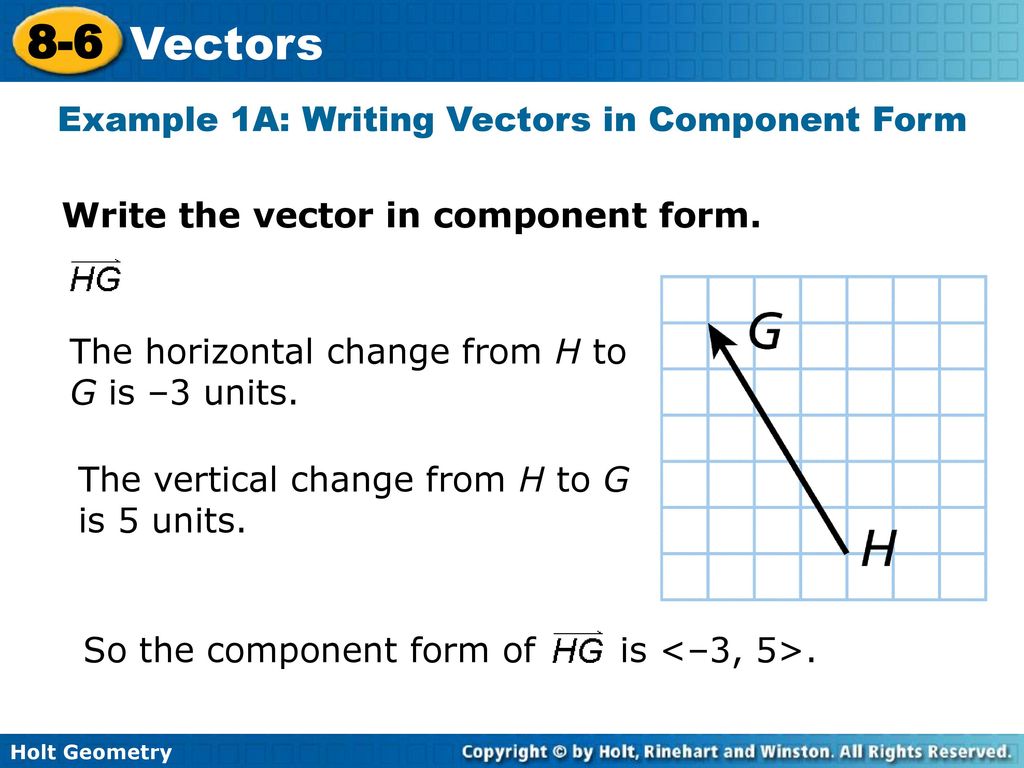

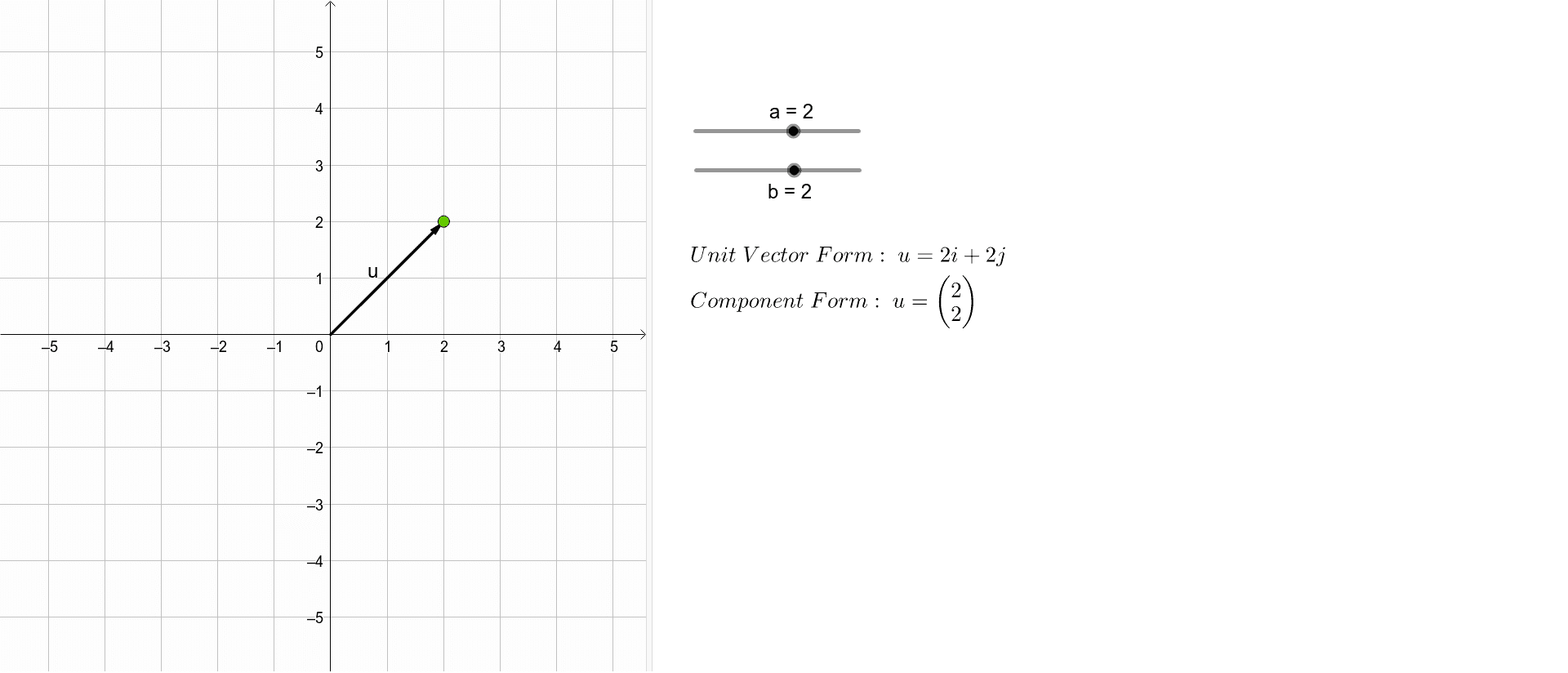

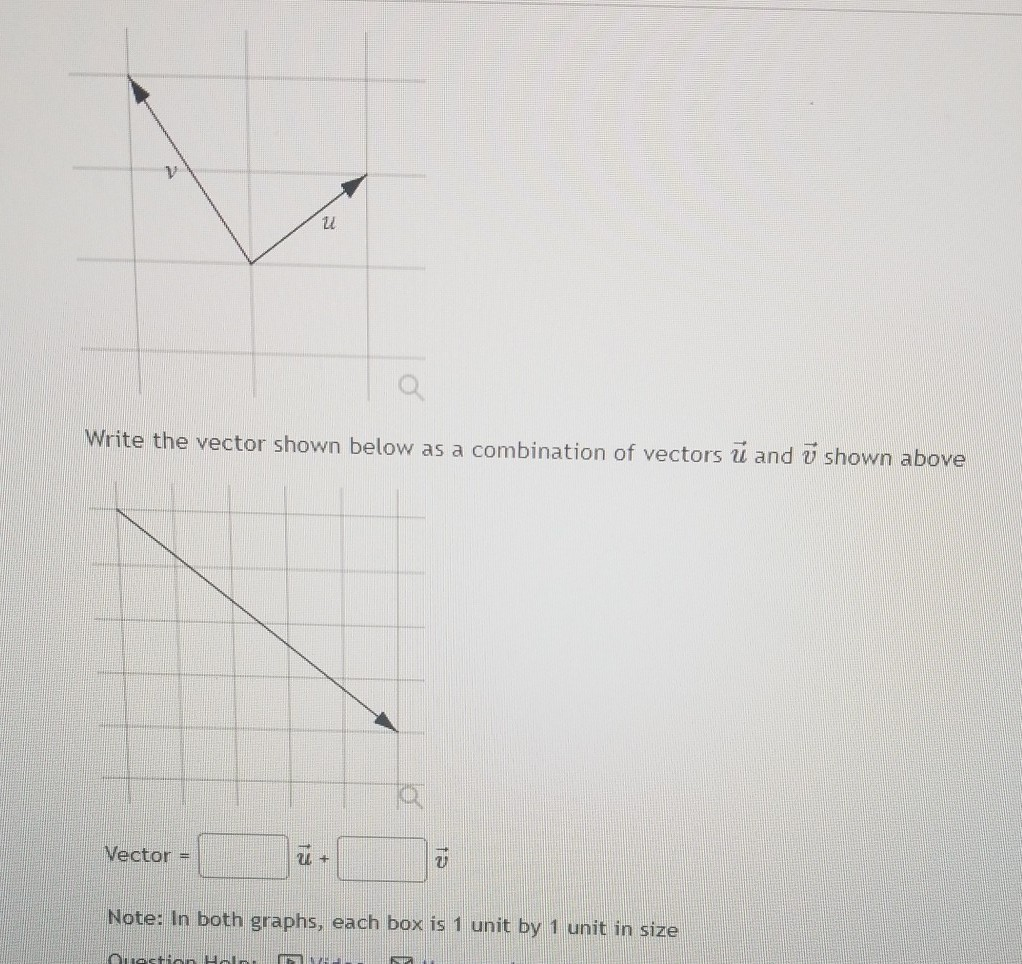

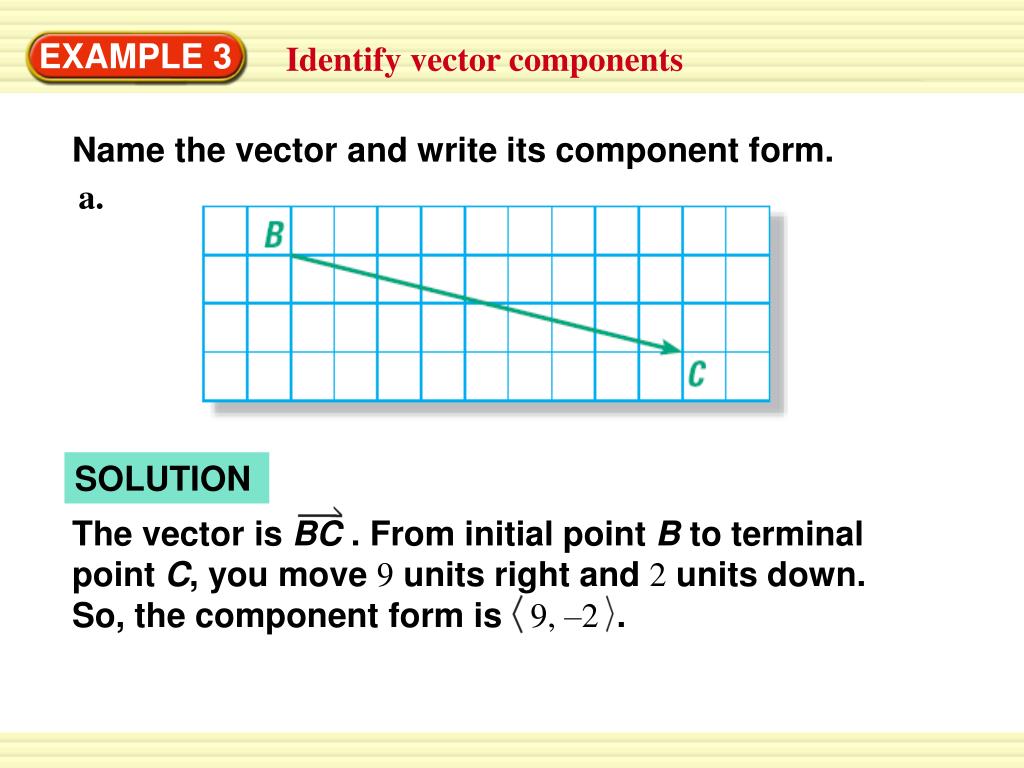

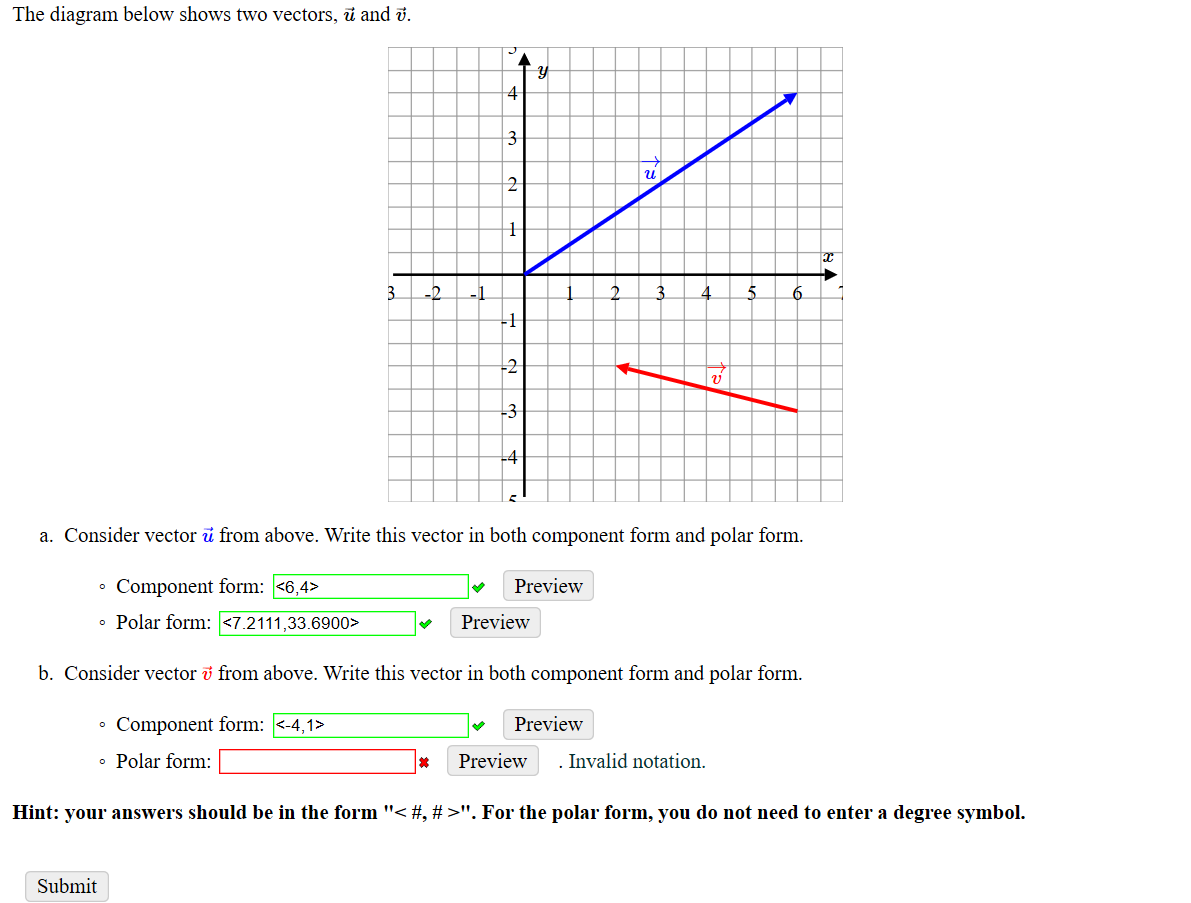

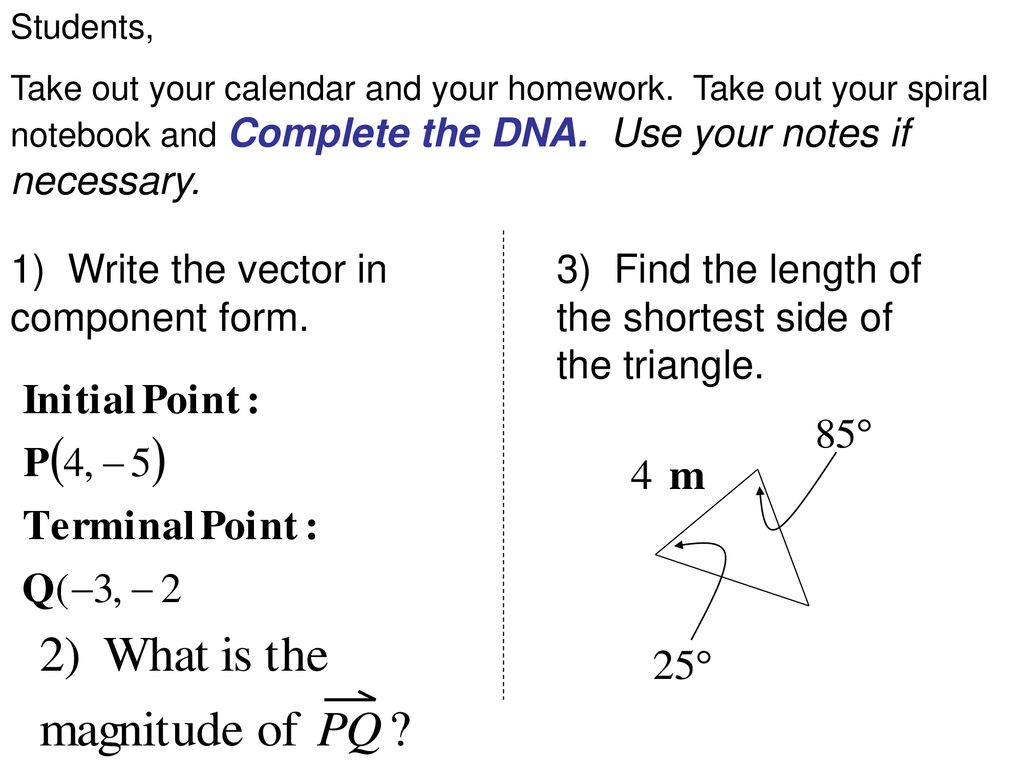

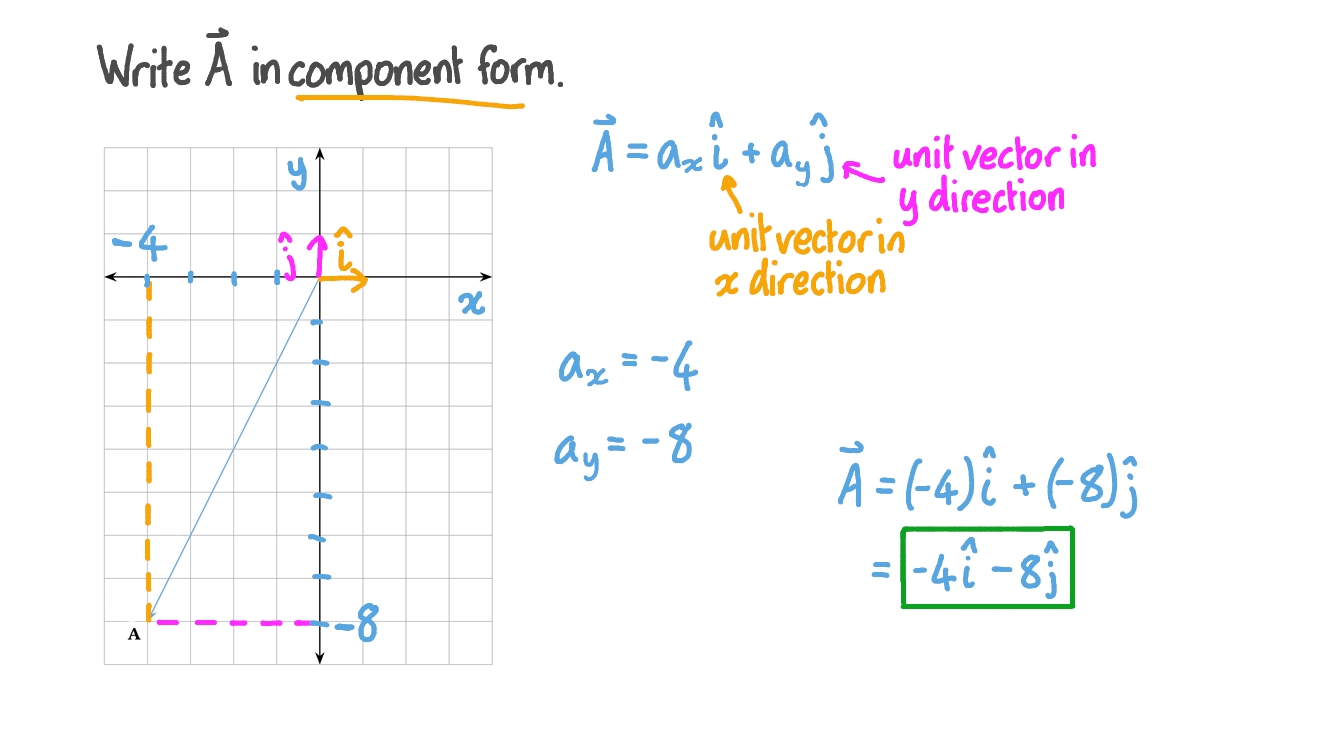

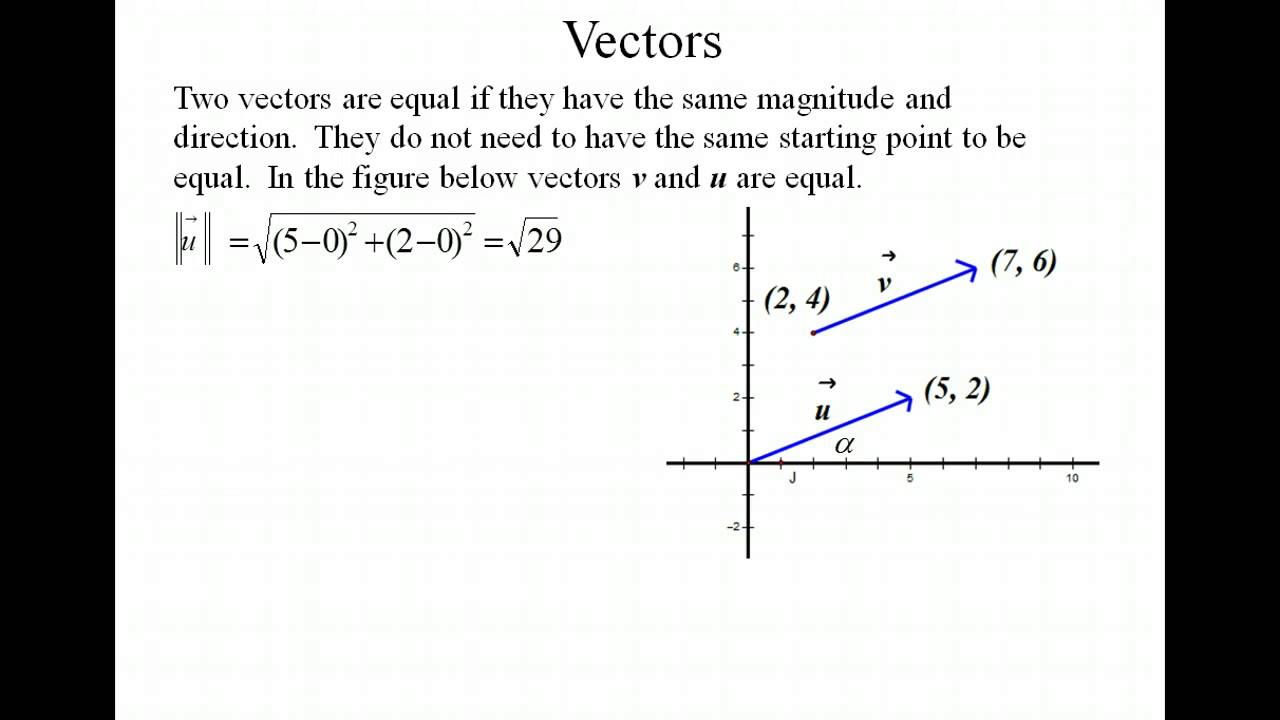

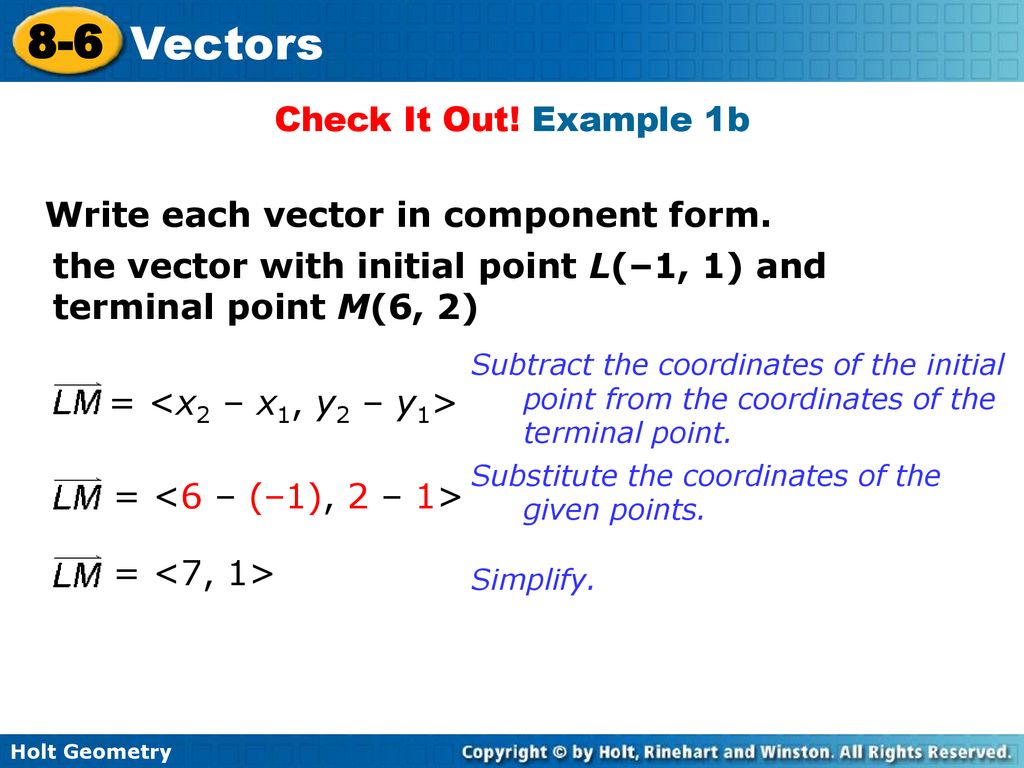

How To Write A Vector In Component Form – How To Write A Vector In Component Form

| Welcome for you to my website, on this time I am going to provide you with in relation to How To Factory Reset Dell Laptop. Now, this is actually the initial picture:

What about picture preceding? is usually in which remarkable???. if you believe therefore, I’l t show you many graphic once again down below:

So, if you’d like to acquire all of these awesome photos related to (How To Write A Vector In Component Form), press save button to save the shots for your personal pc. They are ready for download, if you’d prefer and want to obtain it, click save symbol on the web page, and it will be immediately downloaded to your pc.} Finally if you’d like to get new and the recent graphic related to (How To Write A Vector In Component Form), please follow us on google plus or bookmark this blog, we try our best to present you regular up grade with all new and fresh images. We do hope you enjoy keeping here. For some updates and recent news about (How To Write A Vector In Component Form) graphics, please kindly follow us on tweets, path, Instagram and google plus, or you mark this page on book mark section, We try to give you up grade periodically with all new and fresh pics, enjoy your browsing, and find the right for you.

Thanks for visiting our website, contentabove (How To Write A Vector In Component Form) published . Today we’re excited to declare we have found an extremelyinteresting nicheto be pointed out, that is (How To Write A Vector In Component Form) Lots of people searching for details about(How To Write A Vector In Component Form) and of course one of these is you, is not it?